tg-me.com/r_riscv/3293

Last Update:

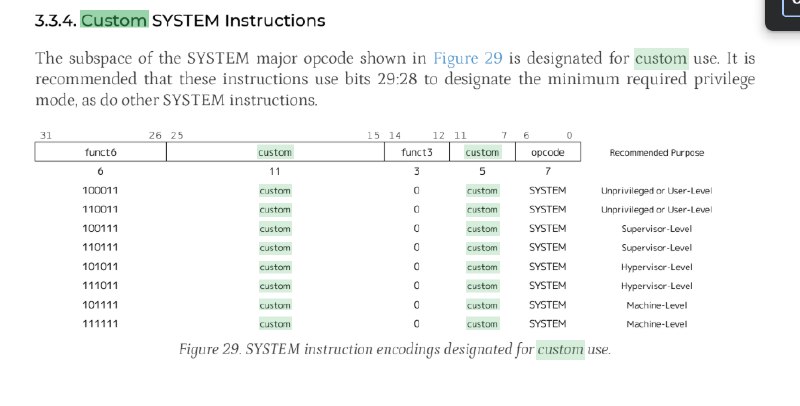

Custom Instruction Opcode Format

I'm having trouble finding a comprehensive description of how to encode/decode custom instructions in the official RISC-V docs or repos.

The opcode table shows :

https://preview.redd.it/4ef6jy09x50f1.png?width=931&format=png&auto=webp&s=bfe664d916a9b8f58f3c0e3a88fcf3b432dea4f7

\- First of all, I'm guessing SYSTEM is `b1110011 - but I could not find it explicitly stated in the above section, so I worked back from other instructions like MRET that also use SYSTEM.

\- I assume I can set bits 25:15 and 11:7 to anything? (e.g immediate value or register select?)

\- (func3 == 0) and (func16 & `b1000111 == `b100011) differentiates custom instructions from other SYSTEM instructions?

I don't think any custom opcodes are defined in the standard machine readable specifications. Are there any good forks that have custom instructions?

(e.g https://github.com/riscv/riscv-opcodes or https://github.com/riscv/sail-riscv )

(I was collecting machine readable specs here https://www.five-embeddev.com/quickref/machine-readable.html and could not find any other examples - are there any good machine readable references for custom opcodes?)

https://redd.it/1kk2grr

@r_riscv

BY RISC-V Reddit

Share with your friend now:

tg-me.com/r_riscv/3293